Un "Field-Programmable Gate-Array" (FPGA) est une puce comprenant des cellules logiques programmables[3] composées (selon leurs programmations) de bascules D, de RAM, ou de "Look-Up Table" (LUT). Configurer un FPGA est le fait d'interconnecter ces cellules logiques et de les programmer, afin de créer un circuit intégré contenant la logique souhaitée.

Cette puce permet de concevoir un ou plusieurs "System-on Chip" (SoC) dont les périphériques sont réalisés grâce aux cellules logiques programmables. En ce qui concerne le logiciel, il existe deux types de processeurs pour les FPGA Xilinx :

- MicroBlaze, qui comme les périphériques est composé des cellules logiques programmables

- PowerPC 405, qui est fondu dans la puce

Les FPGA Xilinx Virtex-II Pro et Virtex-4 FX contiennent un ou plusieurs PowerPC 405 [5]. Ce sont des processeurs IBM 32 bits de type Harvard, c'est-à-dire qu'ils sont munis d'un cache d'instructions séparé du cache de données pour permettre la pseudo-parallélisation[4] des instructions. Ils possèdent chacun leur propre "Memory Management Unit" (MMU), capable de gérer des pages de tailles variables (de 1 Ko à 16 Mo), afin de séparer l'espace d'adressage des processus, apportant ainsi une protection matérielle lors des accès mémoire. Même s'il y a plusieurs PowerPC 405 sur certains modèles de FPGA Xilinx, il n'est pas possible de faire une architecture multi-processeurs puisqu'ils ne possèdent pas d'espion de cache pour assurer la cohérence des données. Il est toutefois possible de les faire interagir entre eux et même de leur faire partager certaines portions de code (voir chapitre B).

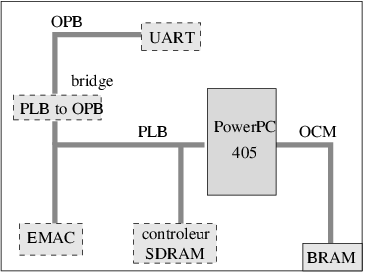

Les périphériques communiquent avec le processeur PowerPC 405 selon l'architecture CoreConnect d'IBM. Cette architecture se compose de trois bus :

bus principal à haut débit permettant d'interfacer directement les périphériques à haute-vitesse avec le processeur

bus secondaire à plus faible débit permettant d'interfacer les périphériques à basse-vitesse avec le bus PLB

ce bus permet de configurer les périphériques tout en économisant la bande passante des bus PLB et OPB

Il existe un autre bus qui se connecte directement au PowerPC 405, mais qui ne fait pas partie de l'architecture CoreConnect, il s'agit du bus "On-Chip Memory" (OCM). Celui-ci permet de connecter directement au processeur la mémoire présente dans la puce. Pour cette démonstration, les blocs de RAM du FPGA (BRAM) seront utilisés avec ce bus OCM.